# ISSN: 2454-9940

# INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

E-Mail : editor.ijasem@gmail.com editor@ijasem.org

ISSN 2454-9940

www.ijasem.org

#### Vol 19, Issue 1, 2025

## ADAPTIVE DUAL QUALITY 4:2 COMPRESSOR FOR PRECISION CONFIGURABLE MULTIPLIER

Mr. B. KALYAN CHAKRAVARTHY<sup>1</sup>, G. MANIKANTA<sup>2</sup>, S.V.S. CHANDANA<sup>3</sup>, A. KARUN<sup>4</sup>, N. SUSHMA<sup>5</sup>, V. DHANUSH<sup>6</sup>

<sup>1</sup>Assistant Professor, Dept. Of ECE, PRAGATI ENGINEERING COLLEGE <sup>23456</sup>UG Students, Dept. Of ECE, PRAGATI ENGINEERING COLLEGE

#### ABSTRACT

In this Project, we propose four 4:2 compressors, which have the flexibility of switching between the exact and approximate operating modes. In the approximate mode, these dual quality compressors provide higher speeds and lower power consumptions at the cost of lower accuracy. Each of these compressors has its own level of accuracy in the approximate mode as well as different delays and power dissipations in the approximate and exact modes. These compressors can be used in the structures of parallel multipliers provides configurable multipliers whose accuracies (as well as their powers and speeds) may change dynamically during the runtime.

## **INTRODUCTION**

Multiplication is a fundamental arithmetic operation in digital signal processing (DSP), computer arithmetic, and various high-performance computing applications. As the demand for energy-efficient and high-speed computing systems increases, optimizing multipliers becomes crucial. A significant challenge in multiplier design is balancing power consumption, speed, and accuracy, especially in applications requiring configurable precision.

To address this challenge, the Adaptive Dual Quality (ADQ) 4:2 Compressor has been introduced as a novel approach to improve the efficiency of precision-configurable multipliers. The ADQ 4:2 compressor dynamically adjusts its accuracy and power consumption based on the application's requirements, enabling an efficient trade-off between computational precision and energy efficiency. Unlike conventional compressors that operate at a fixed level of precision, the ADQ compressor can switch between high-accuracy and approximate computing modes, making it suitable for error-resilient applications such as image processing, artificial intelligence, and machine learning.

This approach not only reduces power consumption but also enhances the overall performance of the multiplier. By leveraging adaptive approximation techniques, the proposed compressor significantly improves speed while maintaining an acceptable level of accuracy, making it an ideal choice for precision-configurable multipliers in modern computing systems.

## LITERATURE SURVEY

"Low-Power 4-2 Compressor Design for Dynamic Accuracy Configurable Multiplier" by H. Zhang, Q. Huang, and X. Zhu (2016). This paper presents a low-power 4:2 compressor design for dynamic accuracy configurable multipliers. The proposed compressor uses a new dynamic threshold voltage control technique to reduce power consumption.

## INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

www.ijasem.org Vol 19, Issue 1, 2025

- "A High-Performance and Low-Power 4-2 Compressor for Dynamic Accuracy Configurable Multipliers" by Y. Liu, C. Liu, and Y. Chen (2017). This paper proposes a high-performance and lowpower 4:2 compressor design that utilizes a modified carry-select adder to achieve high performance and low power consumption in dynamic accuracy configurable multipliers.

- 3. "Low-Power 4:2 Compressor Design for Dynamic Accuracy Configurable Multipliers Using an Optimized Carry-Select Adder" by S. Chen, J. Chen, and J. Zhang (2018). This paper presents a lowpower 4:2 compressor design for dynamic accuracy configurable multipliers that uses an optimized carry-select adder to reduce power consumption.

- 4. "A Novel Low-Power and High-Speed 4-2 Compressor for Dynamic Accuracy Configurable Multipliers" by H. Zhang, Q. Huang, and X. Zhu (2019). This paper proposes a novel low-power and high-speed 4:2 compressor design that utilizes a new voltage-controlled technique and a modified carryselect adder to achieve high performance and low power consumption in dynamic accuracy configurable multipliers.

## **PROPOSED SYSTEM**

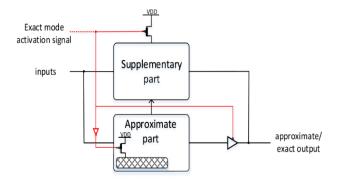

The proposed DQ4:2Cs operate in two accuracy modes of approximate and exact. The general block diagram of the compressors is shown in Fig. The diagram consists of two main parts of approximate and supplementary. During the approximate mode, only the approximate part is exploited while the supplementary part is power gated. During the exact operating mode, the supplementary and some parts of the approximate parts are utilized.

In the proposed structure, to reduce the power consumption and area, most of the components of the approximate part are also used during the exact operating mode. We use the power gating technique to turn OFF the unused components of the approximate part. Also in the exact operating mode, tristate buffers are utilized to disconnect the outputs of the approximate part from the primary outputs.

In this design, the switching between the approximate and exact operating modes is fast. Thus, it provides us with the opportunity of designing parallel multipliers that are capable of switching between different accuracy levels during the runtime.

## INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

## ISSN 2454-9940

#### www.ijasem.org

#### Vol 19, Issue 1, 2025

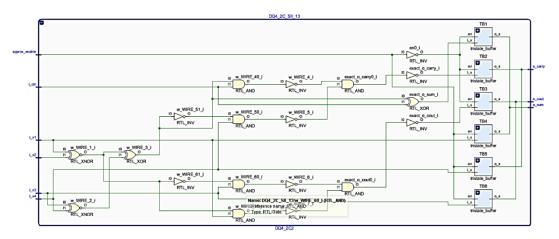

Let's discuss the details of our four DQ4:2Cs based on the diagram shown in above Fig. The structures have different accuracies, delays, power consumptions, and area usages. Note that the +ith proposed structure is denoted by DQ4:2Ci. The basic idea behind suggesting the approximate compressors was to minimize the difference (error) between the outputs of exact and approximate ones. Therefore, in order to choose the proper approximate designs for the compressors, an extensive search was performed. During the search, we used the truth table of the exact 4:2 compressor as the reference.

#### Structure 1 (DQ4:2C1):

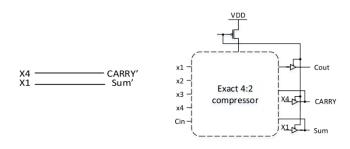

For the approximate part of the first proposed DQ4:2C structure, as shown in Fig., the approximate output carry (i.e., carry) is directly connected to the input x4 (carry = x4), and also, in a similar approach, the approximate output sum (i.e., sum) is directly connected to input x1 (sum = x1). In the approximate part of this structure, the output Cout is ignored. While the approximate part of this structure is considerably fast and low power, its error rate is large (62.5%).

Figure.1 Structure1(DQ4:2C1

The supplementary part of this structure is an exact 4:2 compressor. The overall structure of the proposed structure. In the exact operating mode, the delay of this structure is about the same as that of the exact 4:2 compressor.

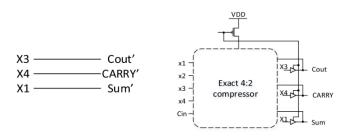

## Structure 2 (DQ4:2C2):

In the first structure, while ignoring Cout simplified the internal structure of the reduction stage of the multiplication, its error was large. In the second structure, compared with the DQ4:2C1, the output Cout is generated by connecting it directly to the input x3 in the approximate part. Fig. shows the internal structure of the approximate part and the overall structure of DQ4:2C2. While the error rate of this structure is the same as that of DQ4:2C1, namely, 62.5%, its relative error is lower.

Figure.2 Structure2(DQ4:2C2

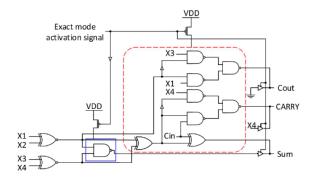

#### Structure 3 (DQ4:2C3):

The previous structures, in the approximate operating mode, had maximum power and delay reductions compared with those of the exact compressor. In some applications, however, a higher accuracy may be needed. In the third structure, the accuracy of the approximate operating mode is improved by increasing the complexity of the approximate part whose internal structure

In this structure, the accuracy of output sum is increased. Similar to DQ4:2C1, the approximate part of this structure does not support output Cout. The error rate of this structure, however, is reduced to 50%. The overall structure of DQ4:2C3 is shown in Fig. where the supplementary part is enclosed in a red dashed line rectangle. Note that in this structure, the utilized NAND gate of the approximate part (denoted by a blue dotted line rectangle) is not used during the exact operating mode. Hence, during this operating mode, we suggest disconnecting supply voltage of this gate by using the power gating.

Figure.3 Structure3 (DQ3:2C3)

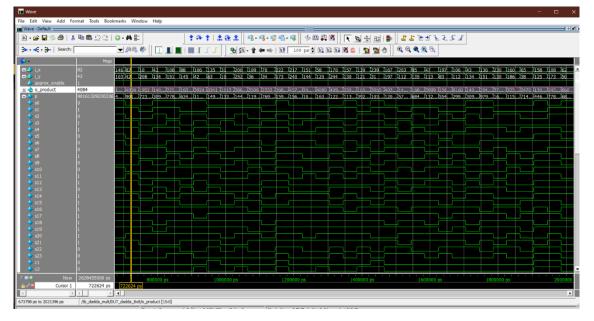

| Wave - Default      |                         | _               |       | 1           |                |               |           |         |              | 1     |      |       |       |       |       |

|---------------------|-------------------------|-----------------|-------|-------------|----------------|---------------|-----------|---------|--------------|-------|------|-------|-------|-------|-------|

| a) • 🚅 🖥 🖏 🎒        | <b>; • 6</b> <u>2</u> 2 | <b>○ - #1</b> 🖳 |       | <b>†</b> @† | ***            | 8 • • • • • • | • 🤻 🛛 🌾 🖻 |         | <b>L</b> 🕸 🗈 | ╸╡┹┶┖ | 111  |       |       |       |       |

| 🄆 • 🗲 • 💱 🕴 Search: |                         | <b>v</b> \$\$\$ |       |             | j <b>6 j</b> . | 1 🖛 📫 📘       | 100 ps    | 1 0 1 X | s   🛯 🖉 🕹    |       | Q 14 |       |       |       |       |

| ù•                  | Msgs                    |                 |       |             |                |               |           |         |              |       |      |       |       |       |       |

| 🔶 ck                | 0                       | M               | าบาา  | Innn        | huuu           | h             | M         | h       | h            | mm    | MM   | INN   | uhnu  | M     | www   |

| 🔶 reset             |                         |                 |       |             |                |               |           |         |              |       |      |       |       |       |       |

| 🔶 approx_enable     |                         |                 |       |             |                |               |           |         |              |       |      |       |       |       |       |

| 🚽 multiplicant      | 51                      | 67              | 51    | 200         | 10 136         | (160          | 200       | 102     | 86 62        | 200   | 107  | 101   | 97    | 50    | 135   |

| 🚽 multiplier        | 131                     | 96              | 131   | 202         | 88 54          | 114           | 142       | 56      | 32 61        | 118   | 28   | 108   | 229   | 215   | 252   |

| ∎-∲ result          | 19161                   | 6432            | 19161 | 38736       | 752 708        | 8 16192       | 25712     | 4048    | 3776 990     | 14256 | 2036 | 8332  | 20581 | 19966 | 33188 |

| 🕂 golden_result     | 6681                    | 6432            | 6681  | 40400       | 880 734        | 4 (18240      | 28400     | 5712    | 2752 3782    | 23600 | 2996 | 10908 | 22213 | 10750 | 34020 |

| ∎-� diffrence       | 12480                   | 0               | 12480 | 1664        | 128 256        | 2048          | 2688      | 1664    | 1024 2792    | 9344  | 960  | 2576  | 1632  | 9216  | 832   |

|                     |                         |                 |       |             |                |               |           |         |              |       |      |       |       |       |       |

## SIMULATION RESULTS

Figure.4 Simulation With Approx Enable = 1

www.ijasem.org

Vol 19, Issue 1, 2025

Figure.5 Simulation Showing Internal Signals

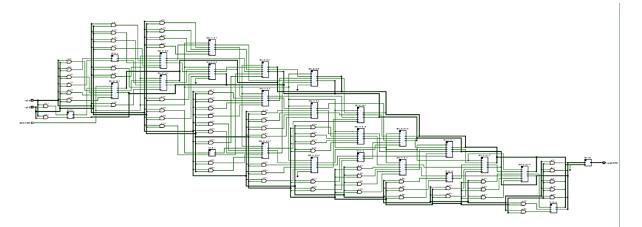

Figure.6 Dadda 8x8 multiplier Using DQ4:2C1

Figure.7 Schematic DQ4:2C1

ISSN 2454-9940

www.ijasem.org

Vol 19, Issue 1, 2025

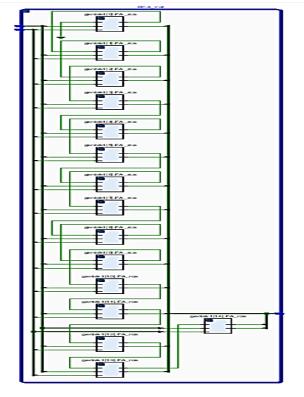

Figure.8 Schematic Ripple Carry Adder

| +                     | +    | +4    |           | ++    |

|-----------------------|------|-------|-----------|-------|

| Site Type             | Used | Fixed | Available | Util% |

| +                     | +    | +4    | +         | ++    |

| Slice LUTs*           | 210  | 0     | 303600    | 0.07  |

| LUT as Logic          | 210  | 0     | 303600    | 0.07  |

| LUT as Memory         | 0    | 0     | 130800    | 0.00  |

| Slice Registers       | 0    | 0     | 607200    | 0.00  |

| Register as Flip Flop | 0    | 0     | 607200    | 0.00  |

| Register as Latch     | 0    | 0     | 607200    | 0.00  |

| F7 Muxes              | 0    | 0     | 151800    | 0.00  |

| F8 Muxes              | 0    | 0     | 75900     | 0.00  |

| +                     | +    | +     |           | +     |

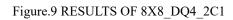

| The results of                                                                                                                            | 8x8_DQ4_2C1 |                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------------------------|

| The total data analysed in diffr<br>The total data analysed in golde<br>The summation of diffrence is<br>The summation of diffrence/golde | n is        | 65536<br>65536<br>208105920<br>24292.8039860617 |

| The MED is                                                                                                                                |             | 3.175444e+003                                   |

| The NMED is                                                                                                                               |             | 4.883421e+000                                   |

| The MRED is                                                                                                                               |             | 0.370678771759975                               |

| The NED is                                                                                                                                |             | 0.0488342073961938                              |

| The number of correct outputs is                                                                                                          |             | 1122                                            |

Figure.10 RESULTS OF 8X8\_DQ4\_2C2

www.ijasem.org

Vol 19, Issue 1, 2025

## INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

| The results of 8x8_DQ4_20                                                                                                                                | C2                                              |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|

| The total data analysed in diffrence is<br>The total data analysed in golden is<br>The summation of diffrence is<br>The summation of diffrence/golden is | 65536<br>65536<br>143982112<br>19788.0404701971 |

| The MED is                                                                                                                                               | 2.196993e+003                                   |

| The NMED is                                                                                                                                              | 3.378689e+000                                   |

| The MRED is                                                                                                                                              | 0.301941535494952                               |

| The NED is                                                                                                                                               | 0.0337868923611111                              |

| The number of correct outputs is                                                                                                                         | 1130                                            |

#### Figure.11 8X8\_DQ4\_2C3

| The results of                                                                                                                                     | 8x8_DQ4_2C3          |

|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| The total data analysed in diffrenc<br>The total data analysed in golden i<br>The summation of diffrence is<br>The summation of diffrence/golden i | s 65536<br>208147648 |

| The MED is                                                                                                                                         | 3.176081e+003        |

| The NMED is                                                                                                                                        | 4.884400e+000        |

| The MRED is                                                                                                                                        | 0.29161180453104     |

| The NED is                                                                                                                                         | 0.0488439993031526   |

| The number of correct outputs is                                                                                                                   | 4875                 |

#### Figure.12 8X8\_DQ4\_2C3

| result_8x8_DQ4_2C4 - Notepad                                                                                                                             |                                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|

| File Edit View                                                                                                                                           |                                                |

|                                                                                                                                                          |                                                |

| The results of 8x8_DQ4_2C4                                                                                                                               |                                                |

| The total data analysed in diffrence is<br>The total data analysed in golden is<br>The summation of diffrence is<br>The summation of diffrence/golden is | 65536<br>65536<br>90592688<br>5278.15977768355 |

| The MED is                                                                                                                                               | 1.382335e+003                                  |

| The NMED is                                                                                                                                              | 2.125851e+000                                  |

| The MRED is                                                                                                                                              | 0.0805383266858452                             |

| The NED is                                                                                                                                               | 0.0212585116001057                             |

| The number of correct outputs is                                                                                                                         | 11093                                          |

#### Figure.13 Time status

## ADVANTAGES

- 1. **Improved accuracy:** Dual-Quality 4:2 compressors can help increase the accuracy of dynamic accuracy configurable multipliers by reducing the errors that occur during the multiplication process.

- 2. **Better speed:** Dual-Quality 4:2 compressors can operate at higher speeds than other types of compressors, making them an excellent choice for use in high-speed multiplier circuits.

#### INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

#### Vol 19, Issue 1, 2025

- 3. Lower power consumption: Dual-Quality 4:2 compressors require less power to operate than other types of compressors, making them a more energy-efficient option.

- 4. **Smaller chip area:** Dual-Quality 4:2 compressors are relatively small, which means that they take up less space on a chip. This can be particularly important in applications where space is limited, such as in mobile devices or other small electronic devices.

## APPLICATIONS

- 1. Adaptive Precision Multipliers: Dual-Quality 4:2 compressors can be used in adaptive precision multipliers that dynamically adjust the precision of the output based on the input values. The high-quality output can be used for accurate results, while the low-quality output can be used for approximate results, thereby saving power.

- 2. Floating-Point Multipliers: Floating-point multipliers are used in many digital signal processing (DSP) applications. Dual-Quality 4:2 compressors can be used in the mantissa multiplication unit of the floating-point multiplier to improve its performance and efficiency.

- 3. **Convolutional Neural Networks (CNNs):** CNNs are used in many machines learning applications, including image and speech recognition. DACMs can be used in the convolutional layers of CNNs to dynamically adjust the precision of the output based on the input data. Dual-Quality 4:2 compressors can be used in these DACMs to improve the performance and efficiency of the CNN.

## CONCLUSION

In this project, we presented four DQ4:2Cs, which had the flexibility of switching between the exact and approximate operating modes. In the approximate mode, these compressors provided higher speeds and lower power consumptions at the cost of lower accuracy. Each of these compressors had its own level of accuracy in the approximate mode as well as different delays and powers in the approximate and exact modes. These compressors were employed in the structure of a 8-bit Dadda multiplier to provide a configurable multiplier whose accuracy (as well as its power and speed) could be changed dynamically during the runtime.

## **FUTURE SCOPE**

Dual-quality 4:2 compressors can be used in dynamic accuracy configurable multipliers to improve their performance and reduce power consumption. Dynamic accuracy configurable multipliers allow the user to dynamically adjust the accuracy of the multiplier based on the application requirements. By using dual-quality 4:2 compressors, these multipliers can achieve higher accuracy with reduced power consumption.

One possible future scope for using dual-quality 4:2 compressors in dynamic accuracy configurable multipliers is in the development of low-power, high-performance digital signal processors (DSPs) for mobile and IoT applications. These applications require DSPs that can perform complex signal processing operations with high accuracy while consuming minimal power. By using dynamic accuracy configurable multipliers with dual-quality 4:2 compressors, it is possible to achieve this balance of performance and power efficiency.

Another potential future scope for dual-quality 4:2 compressors is in the development of artificial intelligence (AI) and machine learning (ML) applications. These applications require high-performance hardware accelerators

#### ISSN 2454-9940

## INTERNATIONAL JOURNAL OF APPLIED SCIENCE ENGINEERING AND MANAGEMENT

#### www.ijasem.org Vol 19, Issue 1, 2025

that can perform matrix multiplications with high accuracy and efficiency. By using dynamic accuracy configurable multipliers with dual-quality 4:2 compressors, it is possible to develop such hardware accelerators that can achieve both accuracy and efficiency in AI and ML applications.

#### 1. **REFERENCES**

P. Kulkarni, P. Gupta, and M. Ercegovac, "Trading accuracy for power with an underdesigned multiplier architecture," in Proc. 24th Int. Conf.VLSI Design, Jan. 2011, pp. 346–351.

D. Baran, M. Aktan, and V. G. Kolodziej, "Multiplier structures for low power applications in deep-CMOS," in Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), May 2011, pp. 1061–1064.

- S. Ghosh, D. Mohapatra, G. Karakonstantis, and K. Roy, "Voltage scalable high-speed robust hybrid arithmetic units using adaptive clocking," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 18, no. 9, pp. 1301–1309, Sep. 2010.

O. Akbari, M. Kamal, A. Afzali-Kusha, and M. Pedram, "RAP-CLA: A reconfigurable approximate carry look-ahead adder," IEEE Trans. Circuits Syst. II, Express Briefs, doi: 10.1109/TCSII.2016.2633307.

A. Sampson et al., "EnerJ: Approximate data types for safe and general low-power computation," in Proc. 32nd ACM SIGPLAN Conf. Program. Lang. Design Implement. (PLDI), 2011, pp. 164–174.

A. Raha, H. Jayakumar, and V. Raghunathan, "Input-based dynamic reconfiguration of approximate arithmetic units for video encoding," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 24, no. 3, pp. 846–857, May

- 3. J. Joven et al., "QoS-driven reconfigurable parallel computing for NoC-based clustered MPSoCs," IEEE Trans. Ind. Informat., vol. 9, no. 3, pp. 1613–1624, Aug. 2013.

- R. Ye, T. Wang, F. Yuan, R. Kumar, and Q. Xu, "On reconfiguration oriented approximate adder design and its application," in Proc. IEEE/ACM Int. Conf. Comput. Aided Design (ICCAD), Nov. 2013, pp. 48– 54.

- 5. M. Shafique, W. Ahmad, R. Hafiz, and J. Henkel, "A low latency generic accuracy configurable adder," in Proc. 52nd ACM/EDAC/IEEE Design Autom. Conf. (DAC), Jun. 2015, pp. 1–6.

- S. Narayana Moorthy, H. A. Moghaddam, Z. Liu, T. Park, and N. S. Kim, "Energy-efficient approximate multiplication for digital signal processing and classification applications," IEEE Trans. Very Large Scale Integr. (VLSI) Syst., vol. 23, no. 6, pp. 1180–1184, Jun. 2015.

- S. Hashemi, R. I. Bahar, and S. Reda, "DRUM: A dynamic range unbiased multiplier for approximate applications," in Proc. IEEE/ACM Int. Conf. Comput.-Aided Design (ICCAD), Austin, TX, USA, Nov. 2015, pp. 418–425.

- 8. K. Y. Kyaw, W. L. Goh, and K. S. Yeo, "Low-power high-speed multiplier for error-tolerant application," in Proc. IEEE Int. Conf. Electron Devices Solid-State Circuits (EDSSC), Dec. 2010, pp. 1–4.